Flip-flop este un termen care se încadrează în electronica digitală și este o componentă electronică care este folosită pentru a stoca un singur bit de informații.

Reprezentarea schematică a flip-flop

- Deoarece Flip Flop este un circuit secvenţial, intrarea sa se bazează pe doi parametri, unul este intrarea curentă, iar celălalt este ieşirea din starea anterioară.

- Are două ieșiri, ambele se completează una cu cealaltă.

- Poate fi într-una din cele două stări stabile, fie 0, fie 1.

Diagrama de bază a Flip Flop

Ce este T Flip Flop?

- T flip flop sau, mai precis, este cunoscut sub denumirea de Toggle Flip Flop, deoarece își poate comuta ieșirea în funcție de intrare.

- T aici reprezintă Comutare .

- Comutarea indică practic că bitul va fi inversat, adică fie de la 1 la 0, fie de la 0 la 1.

- Aici, un impuls de ceas este furnizat pentru a opera acest flop, deci este un flip-flop tactat.

Construcția T Flip Flop

Putem construi T flip în trei moduri și anume:

- Prin utilizarea SR Flip Flops.

- Folosind D Flip Flops.

- Prin utilizarea JK Flip Flops

Modalități de a construi T Flip Flop

Să vedem construcția T Flip Flop folosind SR Flip Flops, care necesită 2 porți AND și 2 porți NOR, așa cum se arată mai jos:

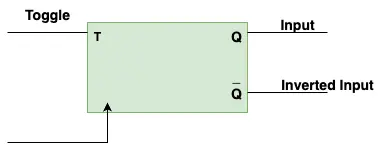

Diagrama bloc de bază a T Flip Flop

Aici diagrama bloc conține intrările de comutare și ceas, Q și Q’ sunt intrările completate.

Funcționarea T Flip Flop

Cazul 1 : Sa spunem, T = 0 iar pulsul ceasului este înalt adică 1, atunci ieșirea ambelor, AND 1, AND 2 va fi 0 , poarta 3 ieșirea va fi Q si asemanator poarta 4 ieșirea va fi Q’ deci ambele valori ale lui Q și Q’ sunt aceleași cu valoarea lor anterioară, ceea ce înseamnă Starea de mentinere .

Cazul 2 : Sa spunem, T=1 , atunci ieșirea ambelor și a porții 1 va fi (T * ceas * Q) , și deoarece T și ceasul ambele sunt 1, atunci ieșirea porții AND 1 va fi Q și, în mod similar, ieșirea porții AND 2 va fi (T * ceas * Q’) adică, Q’ . Acum, ieșirea poarta 3 va fi (Q’+Q)’ și să presupunem că Q’ este zero, atunci ieșirea porții 3 va fi (0+Q)” care înseamnă Q’ și în mod similar ieșirea poarta 4 va fi (Q+Q’)’ și deoarece Q’ este zero, deci ieșirea porții 4 va fi Q’ ceea ce înseamnă 0 întrucât Q’ este zero. Prin urmare, în acest caz putem spune că ieșirea comută, deoarece T=1 .

Tabelul de Adevăr al lui T Flip Flop

- Aici, T este intrarea de comutare, Q este intrarea de stare prezentă, Qt+1 este următoarea ieșire de stare.

- De aici putem vedea că, ori de câte ori Comutare (T) este 0, următoarea ieșire de stare (Qt+1) este aceeași cu intrarea de stare curentă (Q).

- Ori de câte ori Comutarea (T) este 1, următoarea ieșire de stare (Qt+1) va fi complementară a intrării de stare curentă (Q), ceea ce înseamnă că este comutată.

Ecuația caracteristică

- Ecuația caracteristică ne spune despre care va fi următoarea stare de flip flop în ceea ce privește starea prezentă.

- Pentru a obține ecuația caracteristică, se construiește K-Map care va fi prezentată mai jos:

- Dacă rezolvăm K-Map de mai sus, atunci ecuația caracteristică va fi Q(n+1) = TQn’ + T’Qn = T XOR Qn

Tabelul de excitație

Tabelul de excitație spune, în principiu, despre excitația cerută de flip flop pentru a trece de la starea curentă la următoarea stare.

- Aici, ori de câte ori T este 0, Qt+1 este același cu intrarea Q.

- Și, ori de câte ori T este 1, Qt+1 este un compliment de intrare Q.

Aplicații ale T Flip Flop

Există numeroase aplicații ale T Flip Flop în sistemul digital, care sunt enumerate mai jos:

- Contoare : T Flip Flops folosite la contoare. Contoarele numără numărul de evenimente care au loc într-un sistem digital.

- Stocare a datelor : T Flip Flops utilizate pentru a crea memorie care sunt folosite pentru a stoca date, atunci când alimentarea este oprită.

- Circuite logice sincrone : T flip-flops pot fi folosite pentru a implementa circuite logice sincrone, care sunt circuite care efectuează operații pe date binare bazate pe un semnal de ceas. Prin sincronizarea operațiunilor circuitului logic la semnalul de ceas folosind T flip-flops, comportamentul circuitului poate fi făcut previzibil și fiabil.

- Diviziunea în frecvență : Este folosit pentru a împărți frecvența unui semnal de ceas cu 2. Flip-flop-ul își va comuta ieșirea de fiecare dată când semnalul de ceas trece de la mare la scăzut sau de la scăzut la ridicat, împărțind astfel frecvența de ceas la 2.

- Deplasare registre : T flip-flops pot fi utilizate în registrele de deplasare care sunt folosite pentru a deplasa datele binare într-o direcție.

Concluzie

În acest articol pornim de la elementele de bază ale flip-flops, ceea ce sunt de fapt flip flops și apoi am discutat despre T Flip Flops, trei două moduri în care putem construi T Flip Flops, este diagrama bloc de bază, funcționarea T Flip Flop. , este tabelul de adevăr, ecuația caracteristică precum și tabelul de excitație și la final am discutat despre Aplicațiile T Flip Flops.